चिपलेट्सचे आगमन • लेख nown ज्ञानाचा झेस्ट, चिपलेट डिझाइन किट्स 3 डी आयसी विषम एकत्रीकरण | सीमेंस सॉफ्टवेअर

3 डी आयसी विषम एकत्रीकरणासाठी मार्ग मोकळा करण्यासाठी चिपलेट डिझाइन किट वापरणे

Contents

- 1 3 डी आयसी विषम एकत्रीकरणासाठी मार्ग मोकळा करण्यासाठी चिपलेट डिझाइन किट वापरणे

- 1.1 चिप्लेट्सचे आगमन

- 1.2 प्रस्तावना

- 1.3 चिपलेट, क्यूसाको ?

- 1.4 चपलेट्सचे आर्थिक पैलू

- 1.5 दोन उदाहरणे: एएमडी आणि इंटेल (अल्टेरा)

- 1.6 3 डी आयसी विषम एकत्रीकरणासाठी मार्ग मोकळा करण्यासाठी चिपलेट डिझाइन किट वापरणे

- 1.7 यशस्वी 2 साठी इकोसिस्टम तयार करणे.5 डी आणि 3 डी चिपलेट मॉडेल एकत्रीकरण

- 1.8 यशस्वी 2 साठी इकोसिस्टम तयार करणे.5 डी आणि 3 डी चिपलेट मॉडेल एकत्रीकरण

- 1.9 लीक केलेल्या प्रतिमेत जीपीयू एएमडी रॅडियनसाठी चिपलेटची महत्वाकांक्षी रचना दिसून येते

- 1.10 लीक केलेल्या प्रतिमेत जीपीयू एएमडी रॅडियनसाठी चिपलेटची महत्वाकांक्षी रचना दिसून येते

काही वर्षांनंतर, प्रथम प्रोसेसर विशेषत: इंटेल 4004 सह दिसू लागले, आज तुलनेने सोपे. मग प्रोसेसर अधिक जटिल झाले.

चिप्लेट्सचे आगमन

जेझेडडीएसमधील चर्चेनंतर आणि डिसऑर्डरवर, मी स्वत: ला सांगितले की चिपलेटवर लेख लिहिणे सर्वात मोठ्या संख्येसाठी फायदेशीर ठरेल. आणि जेझेडडीएसचे काय होऊ शकते याच्या विरूद्ध लेखी ट्रॅक ठेवेल

खूप लांब तिकीट लिहिण्याऐवजी मी लेखाचे स्वरूप तपशीलात थोडे अधिक मिळविण्यासाठी प्राधान्य दिले. मला आशा आहे की चपलेट्स काय आहेत, हे तंत्रज्ञान का तयार केले गेले आहे आणि येणा years ्या काही वर्षांत त्याचा विकास का होईल.

- प्रस्तावना

- चिपलेट, क्यूसाको ?

- चपलेट्सचे आर्थिक पैलू

- दोन उदाहरणे: एएमडी आणि इंटेल (अल्टेरा)

प्रस्तावना

हा लेख संगणकाच्या संगणक, इलेक्ट्रॉनिक आणि आर्किटेक्चर संकल्पनांबद्दल बोलतो जो विशिष्ट वाचकांसाठी पुरेसा प्रगत असू शकतो. आम्ही ज्या गोष्टींबद्दल बोलत आहोत त्याबद्दल थोडे चांगले समजून घेण्यासाठी मी या प्रस्तावनेत थोडे लोकप्रिय करतो.

शुद्धीकरणासाठी, शॉर्टकट तयार केले जातील, हे लोकप्रियता समजण्यास सुलभ करण्यासाठी स्वेच्छेने चुकीची माहिती असू शकते.

चिपलेट, क्यूसाको ?

चला सर्वात कठीण सह प्रारंभ करूया, चिपलेट म्हणजे काय हे परिभाषित करा !

खरंच चिपलेट हा शब्द १ 1970 s० च्या दशकात दिसला परंतु त्याचा उपयोग प्रामुख्याने अलिकडच्या वर्षांत झाला आहे, ज्यांना जटिल प्रोसेसर किंवा एफपीजीए सारख्या इलेक्ट्रॉनिक चिप्समध्ये रस आहे (ज्यांचे अंतर्गत तार्किक दरवाजे पुनर्प्रक्रिया केले जाऊ शकतात). इतरांसाठी, खोलीच्या तळाशी, आपण कदाचित हा शब्द कधीही ऐकला नसेल, आम्ही त्यावर उपाय करू !

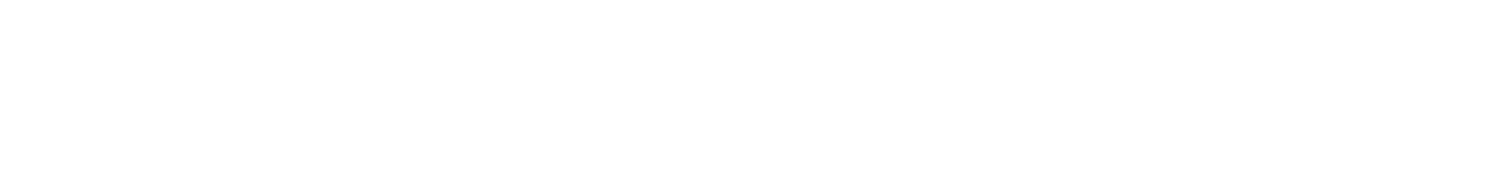

इलेक्ट्रॉनिक चिप म्हणजे काय या आधारावर परत जाऊया: कोरलेल्या सिलिकॉनचा एक तुकडा (प्रसिद्ध ट्रान्झिस्टर) जो एखाद्या प्रकरणात एन्केप्युलेटेड आहे. क्रॉसिंग घटकांसह, लहान सोन्याचे किंवा चांदीचे धागे घटकाचे पाय सिलिकॉनच्या तुकड्यावर जोडतात. सुरुवातीस, चिप्स बर्यापैकी खडबडीत ठराव (आजच्या तुलनेत) कोरलेल्या ट्रान्झिस्टरपासून बनलेल्या आहेत आणि कार्ये मूलभूत होती: तार्किक दरवाजे, ऑपरेशनल एम्पलीफायर इ. तथापि, सूक्ष्मकरणाच्या बाबतीत ही आधीच प्रचंड प्रगती होती !

त्यावेळी घटकांमध्ये पाय ओलांडत होते आणि सिलिकॉन चिपला या पायांशी जोडणे आवश्यक आहे. हे चांदी किंवा सोन्याच्या पातळ मुलांनी बनविलेले आहे जे चिप आणि केसांच्या आत असलेल्या पायांच्या दरम्यान वेल्डेड केलेले आहे.

काही वर्षांनंतर, प्रथम प्रोसेसर विशेषत: इंटेल 4004 सह दिसू लागले, आज तुलनेने सोपे. मग प्रोसेसर अधिक जटिल झाले.

१ 1970 s० च्या दशकापासून, आयबीएमने एमसीएम घटक विकसित केले (मल्टी-चोडू) एकाच प्रकरणात अनेक सिलिकॉन चिप्ससह. परंतु हे तंत्रज्ञान प्रामुख्याने 90 च्या दशकाच्या उत्तरार्धात विकसित होईल. आम्ही 1995 मध्ये रिलीझ केलेल्या इंटेलच्या पेंटियम प्रो लक्षात घेऊ शकतो. या प्रोसेसरमध्ये दोन सिलिकॉन चिप्स समाविष्ट आहेत: एक प्रोसेसरसाठी काटेकोरपणे बोलण्यासाठी आणि दुसरे एल 2 कॅशे मेमरीसाठी (प्रोसेसर आणि रॅम दरम्यान बफर मेमरी, बरेच वेगवान परंतु अधिक महाग कारण प्रोसेसरसह कोरलेले).

जसे आपण फोटोमध्ये पाहू शकतो, दोन चिप्सने साधारणपणे समान आकाराचे आकार दिले आहेत आणि इंटेलने कॅशे एल 2 चे अनेक आकार दिले आहेत. कॅशे मेमरी प्रोसेसर विभक्त करण्याचा फायदा प्रकरणात भिन्न कॅशे मेमरी आकारांची ऑफर देताना प्रोसेसर चिपवर स्केल सेव्ह करण्यास सक्षम असेल.

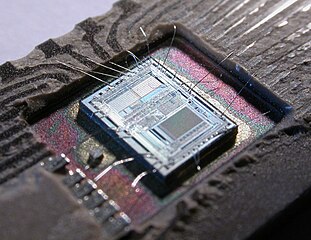

आयबीएमने एमसीएम घटक विकसित केले तरीही या प्रकारचे घटक तुलनेने अविकसित राहतात. 2004 मध्ये रिलीज झालेल्या आयबीएमच्या पॉवर 5 लक्षात घ्या ज्यामध्ये कॅशे एल 3 मेमरी चिपसह चार प्रोसेसर चौरस दिसतात. पिसूंचे परस्पर संबंध प्रकरणात केले जाते.

आज तंत्रज्ञान विकसित झाले आहे आणि एमसीएम चिप्स एएमडी प्रोसेसरसह ग्राहक उत्पादनांमध्ये उपस्थित आहेत. येथे आम्ही एक ईपीवायसी 7702 प्रोसेसर (ऑगस्ट 2019 मध्ये रिलीझ केलेला) 9 इंटरकनेक्ट सिलिकॉन चिप्सचा बनलेला पाहू शकतो: कोर आणि कॅशे मेमरी असलेली 8 चिप्स आणि इतर 8 ला जोडणारी एक मध्यवर्ती चिप आणि जी डीडीआर तसेच सिग्नल डी ‘प्रवेशद्वार/ व्यवस्थापित करते. बाहेर पडा (सटा, पीसीआय एक्सप्रेस, यूएसबी, इ.)).

पण मला सांगा जेमी, एक चिपलेट म्हणजे काय ?

अहो, मी थोडेसे व्युत्पन्न केले

खरं तर एक चिपलेट एमसीएममध्ये उपस्थित असलेल्या सिलिकॉन चिप्सपैकी एक आहे. एक चिपलेट इतर चिपलेट्ससह परस्पर जोडलेले आहे. होय हे तुलनेने सोपे आहे परंतु आपल्याला समजण्यासाठी काही छान फोटो दर्शवावे लागले

तरीही चिप्लट्सच्या अर्थावर थोडे अधिक अचूक असावे, अनेक वेगवेगळ्या चिप्स एकत्र जोडण्याची कल्पना आवश्यक नाही. जेनेरिक चिपची एक कल्पना देखील आहे जी पुन्हा वापरली जाऊ शकते आणि विशिष्ट प्रोसेसर संदर्भात समर्पित नाही.

चपलेट्सचे आर्थिक पैलू

या परिचयानंतर प्रतिमा असताना, आता आपण समजूया. हे करण्यासाठी, इलेक्ट्रॉनिक पिसू तयार करण्याच्या प्रक्रियेकडे परत जाणे आवश्यक आहे.

आर्मचेअरमध्ये आरामात बसा कारण वालुकामय समुद्रकाठची सहल लांब असेल

नाही, थांबा !

आम्ही सिलिकॉनच्या निर्मितीचा संपूर्ण भाग खर्च करू. पिसूंचे वितरण म्हणजे आम्हाला काय आवडते ते आहे (मरणार) सिलिकॉन केकवर (वेफर) आणि विशेषत: खोदकाम करणार्या बारीकसारीक वाढीसह उत्पन्नाची उत्क्रांती.

परंतु उत्पन्नाच्या या पैलूआधी आपण मरण्याच्या जास्तीत जास्त भौतिक आकाराबद्दल बोलणे आवश्यक आहे. खरंच, सिलिकॉन पॅनकेकवर चिपची समान रचना बर्याच वेळा पुनरावृत्ती होते (दहापट किंवा शंभर वेळा). या डिझाइनची छाप अल्ट्राव्हायोलेट लाइटद्वारे ऑप्टिकली केली जाते. तथापि तेथे लेन्स आणि ऑप्टिकल यंत्रणेचा संपूर्ण संच आहे जो संपूर्ण सिलिकॉन केकवर एकाच मरणास खोदण्यास प्रतिबंधित करतो.

आम्ही जितके अधिक पिसूला गुंतागुंत करतो तितके आम्हाला ट्रान्झिस्टर घालायचे आहेत, म्हणून आपण एकतर चिपचा आकार वाढविला पाहिजे किंवा त्याच पृष्ठभागावर अधिक ट्रान्झिस्टर बसविण्यासाठी खोदकाम करण्याची चव वाढविली पाहिजे. परंतु तेथे इतरही अडचणी आणि मर्यादा जाणवल्या आहेत.

म्हणूनच चिपलेटचे तत्त्व या मर्यादांना मागे टाकण्यास मनोरंजक आहे: अधिक जटिल चिप बनविण्यासाठी अनेक लहान सिलिकम चिप्स वापरा परंतु अखंड मार्गाने कोरणे अशक्य आहे.

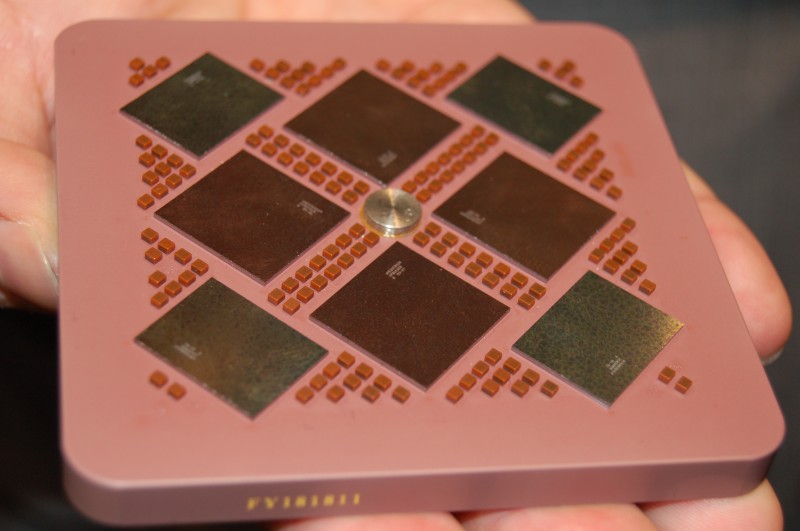

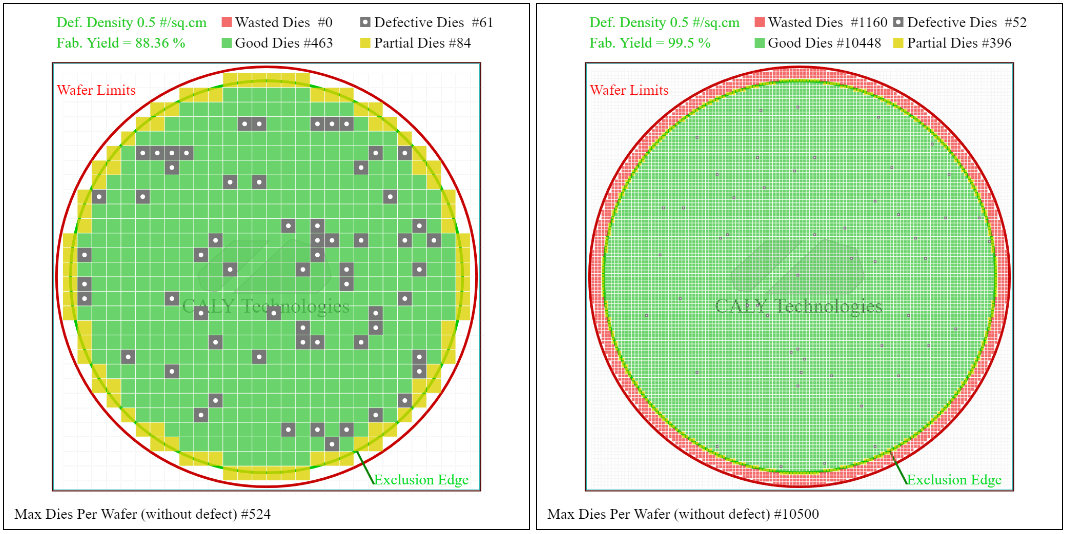

आता परत उत्पन्न (उत्पन्न इंग्रजी मध्ये). प्रथम, वेफर्स आकारात गोल आहेत आणि आम्हाला ते आयताकृती चिप्ससह कोरू इच्छित आहे. संपूर्ण सिलिकॉन वापरला जात नाही. परंतु कडा वर जितके लहान मरणार तितकेच आणि आम्ही जितके अधिक मरणार तितकेच. हे व्हिडिओ गेममध्ये अलियासिंगसारखेच तत्त्व आहे: गोल आकार तयार करण्यासाठी जितके जास्त पिक्सेल वापरले जातात तितके लहान आणि कमी आपल्याला निकिंगची जाणीव होते.

वरील उदाहरणात, आम्ही एकूण मृत्यूच्या संख्येवर (चांगले आणि पूर्वाग्रह) आंशिक मरण नोंदविल्यास आम्ही 13 चे प्रमाण प्राप्त करतो.5 × 5 मिमी आणि 3 च्या मृत्यूच्या बाबतीत 8 %.1 × 1 मिमीच्या बाबतीत 6 % मरण पावले. जितके लहान मरणार असेल तितके अधिक वैध मरणास कडा वर येऊ शकते, ज्यामुळे उत्पन्न वाढते.

आपण वेफरच्या मध्यभागी एक मोठे डाय मिश्रण देखील बनवू शकता आणि अलियासिंगमुळे उत्पन्न अनुकूल करण्यासाठी कडा वर लहान मरणाचा वापर करू शकता.

जमी म्हणा, आयताकृती पिसू बनवण्यासाठी आम्ही गोल वेफर्स का वापरतो? ?

बरं हे सिलिकॉन बनवण्याच्या पद्धतीमुळे आहे जे स्झोक्रल्स्की प्रक्रिया म्हणतात जे सिलेंडर्सच्या रूपात सिलिकॉन देते, देण्यासाठी अगदी बारीक तुकडे केले वेफर.

दुसरे म्हणजे, वेफरवर दिसू शकणार्या दोषांमुळे उत्पन्नावर परिणाम होतो. आपण वेफरवर पडलेल्या धूळ धान्यबद्दल विचार करू शकता.

मी 0 ची फॉल्ट घनता जोडून मागील उदाहरण पुन्हा सुरू केले.प्रति सेमी 5. आता तुलना करा उत्पन्न उत्पादन जे कार्यात्मक मृत्यूची संख्या आणि उत्पादित उत्पादनांच्या एकूण संख्येच्या दरम्यानच्या प्रमाणात संबंधित आहे. 5 × 5 मिमी मरणाच्या बाबतीत, उत्पन्न 88 आहे.4 % तर 1 × 1 मिमी मरण पावले तर उत्पन्न 99 आहे.5 %.

म्हणूनच इलेक्ट्रॉनिक पिसूंचे उत्पादन अनुकूलित करण्यासाठी लहान मृत्यू होणे दुप्पट मनोरंजक आहे. तथापि, कित्येक लहान चिप्समध्ये एक जटिल चिप कापण्यासाठी या भिन्न चिप्स त्यांच्या दरम्यान संप्रेषण करणे आवश्यक आहे, म्हणूनच आम्ही अतिरिक्त जागा घेण्यासाठी येणार्या संप्रेषण घटक जोडले पाहिजेत आणि अतिरिक्त ऊर्जा वापरली पाहिजे.

याव्यतिरिक्त, चिपलेट्सचा वापर केल्यामुळे कार्यक्षमतेसह अंतिम चिपच्या किंमतींमध्ये बदल करण्याची परवानगी देणारी कार्ये नुसार खोदण्याच्या वेगवेगळ्या दंडांचा मृत्यू वापरणे शक्य होते.

शेवटी, पाहण्याची आणखी एक आर्थिक बाब म्हणजे नवीन वैशिष्ट्ये विकसित करण्याची जटिलता. यात विशिष्ट कंपन्या (किंवा सुरुवातीच्या वेळी स्टार्ट-अप) बौद्धिक मालमत्ता ब्लॉक्स (फंक्शन्स) वापरण्यास तयार आहेत. उदाहरणार्थ, पीसीआय एक्सप्रेस, यूएसबी किंवा डीडीआर कंट्रोलर्स सारख्या कार्यांसाठी मृत्यू खरेदी करताना प्रोसेसर निर्माता प्रोसेसरच्या विकासावर लक्ष केंद्रित करण्यास सक्षम असेल.

वेगवेगळ्या उत्पादकांकडून येणा chip ्या चिपलेट्सची इंटरऑपरेबिलिटी सुलभ करण्यासाठी, इंटेल, एएमडी, एआरएम, क्वालकॉम, सॅमसंग किंवा टीएसएमसी सारख्या प्रमुख खेळाडूंनी चिपलेट्स, यूसीआय (यूसीआय) दरम्यान संप्रेषण मानक तयार केले आहे (युनिव्हर्सल चिपलेट इंटरकनेक्ट एक्सप्रेस)).

दोन उदाहरणे: एएमडी आणि इंटेल (अल्टेरा)

एएमडी एपीसी

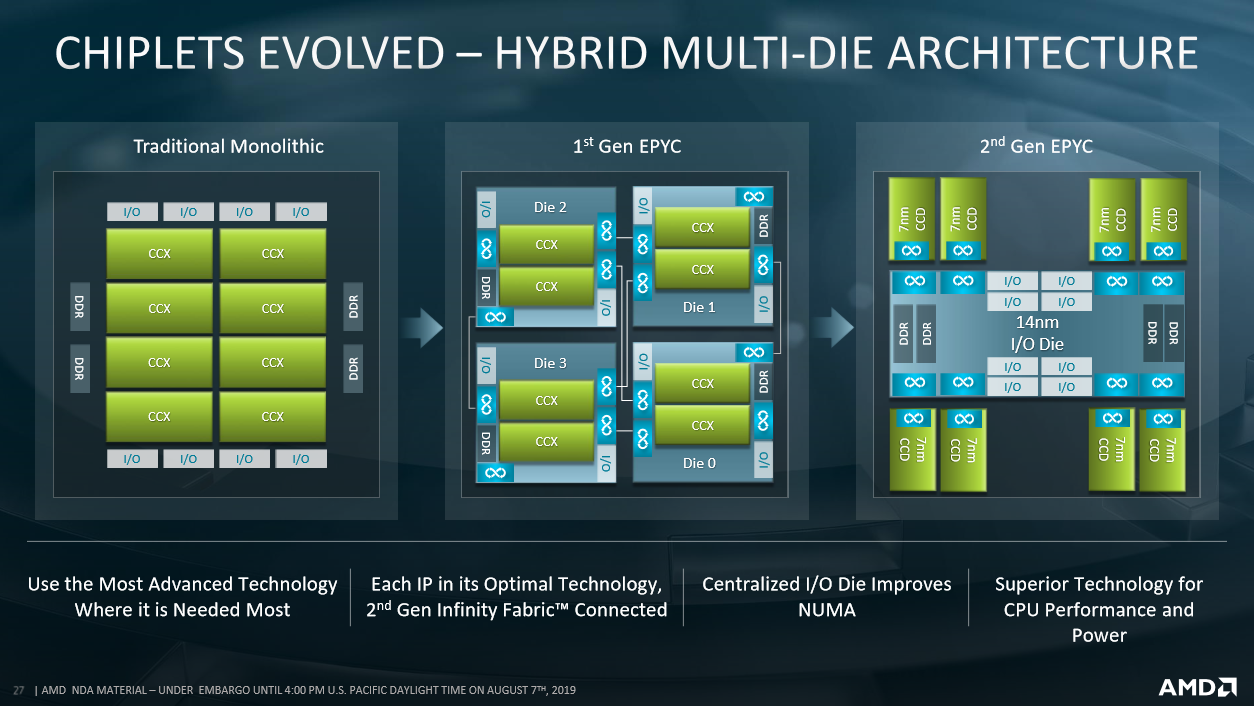

आज अधिकाधिक प्रोसेसर हे चपलेट तंत्र वापरतात. एएमडी ईपीवायसी प्रोसेसरच्या पहिल्या पिढीपासून चपलेट्स वापरते, जिथे भिन्न अंतःकरणे एकत्र जोडल्या जातातअनंत फॅब्रिक.

ईपीवायसी प्रोसेसरच्या पहिल्या पिढीमध्ये मृत्यूचा एक संच दिसला जो संपूर्ण प्रोसेसर एकत्रितपणे जोडला जाऊ शकतोअनंत फॅब्रिक फाटणे. चपलेट्स म्हणून एक प्रकारचे लहान स्वायत्त प्रोसेसर होते: प्रत्येक डायने त्याच्या नोंदी/आउटपुट व्यवस्थापित केल्या आणि त्याचे डीडीआर कंट्रोलर होते.

या मरण पावले किंवा त्याऐवजी चिपल्ट्स दोन आहेत कोर कंप्यूट कॉम्प्लेक्स (सीसीएक्स, कॅशे मेमरीसह चार कोरचा एक संच) तसेच डीडीआर कंट्रोलर, इनपुट/आउटपुट व्यवस्थापित करते (उदाहरणार्थ पीसीआय एक्सप्रेस) आणि यासाठी संप्रेषण मॉड्यूल आहेतअनंत फॅब्रिक.

लहान सूक्ष्मता, प्रथम पिढीच्या ईपीवायसीवर नेहमीच चार चिपलेट असतात. अंतःकरणाची संख्या बदलण्यासाठी, एएमडी सीसीएक्सच्या आत अंतःकरणे निष्क्रिय करते. उदाहरणार्थ 24 कोरे आहेत, सीसीएक्समध्ये केवळ 3 सक्रिय कोर आहेत

या पहिल्या पिढीमुळे चिप्लट्सच्या तत्त्वाचा वापर मोठ्या मोनोलिथिक डाय विकसित करण्याऐवजी एक प्रकारची प्रत/मरण पावला.

दुसर्या पिढीसाठी, एएमडी संकल्पना थोडी पुढे ढकलते. खरंच, सीसीएक्स आता स्वतंत्र आहेत, ए मध्ये जोड्यांमध्ये गटबद्ध आहेत कोअर कॉम्प्यूट डाय (सीसीडी) जोडलेले अनंत फॅब्रिक डीडीआर व्यवस्थापित करण्यासाठी मरण्यासाठी आणि नोंदी/बाहेर पडतात मी/ओ मरणार (आयओडी).

एएमडी फंक्शन्सपासून वाढलेल्या विभक्ततेचा पूर्णपणे शोषण करते. खरंच सीसीडी 7 एनएम मध्ये कोरलेली आहे तर आयओडी 14 एनएम मध्ये कोरलेली आहे.

एएमडी सादरीकरणाच्या खाली ईपीवायसी प्रोसेसरच्या चिपलेटमधील रस्ता सारांशित.

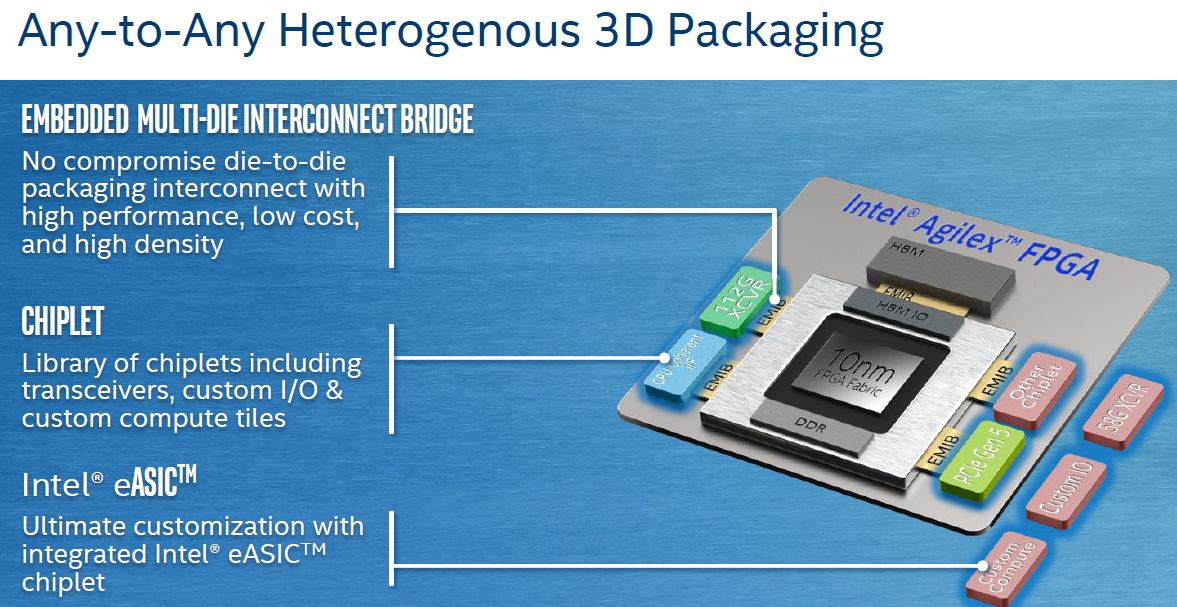

इंटेल एफपीजीए (अल्टेरा)

इंटेल प्रोसेसर नेहमीच काही अपवाद वगळता अखंड चिप्स असतात कारण आम्ही या लेखाच्या सुरूवातीस पाहू शकतो. तरीही इंटेल एफपीजीए (रीकॉन्फिगर करण्यायोग्य एफपीजीए) मध्ये क्षेत्र नवीनतम पिढी, अॅगिलेक्ससाठी चिपलेट्स वापरते.

हे चिप्लट्स प्रामुख्याने वापरल्या जाणार्या ट्रान्ससेन्सच्या प्रकाराची (वेगवान दुवे) चिंता करतात आणि म्हणतात फरशा. जर इंटेलने या टाइलमधून पूर्वनिर्धारित श्रेणी दिली तर आपल्या स्वतःच्या गरजा भागविणे शक्य आहे.

फरशा ट्रान्ससीव्हर्सच्या जास्तीत जास्त वेग आणि समर्थित प्रोटोकॉल (इथरनेट, पीसीआय एक्सप्रेस इ.) द्वारे विभाजित केल्या आहेत.): पीसाठी 16 ग्रॅम, एचसाठी 28 जी, आर साठी 32 जी, इ.

इंटेल भविष्यासाठी अतिरिक्त कार्ये प्रदान करेल अशा सानुकूलित चिपलेट्स कनेक्ट करण्याची शक्यता देखील दर्शवते. सध्या कंपन्यांनी एडीसी/डीएसी (जॅरिएट टेक्नोलॉजीज) चिपलेट तसेच आणखी एक ऑप्टिकल कनेक्शन (आयर लॅब) जाहीर केले आहे.

शेवटी आपण चिप्सवर विश्वास ठेवू नये अखंड मृत आहेत. त्यांचे नेहमीच फायदे असतात, विशेषत: अंतर्गत संप्रेषण आणि विलंब या दृष्टीने, जे मोठ्या आकाराच्या चिप्स आवश्यक असलेल्या विशिष्ट अनुप्रयोगांसाठी गंभीर असू शकतात.

ब्रॉडकॉम आणि त्याच्या स्विच 400 जी चिप्सची ही घटना आहे ज्याची निवड या व्हिडिओमध्ये डिझाइनरने स्पष्ट केली आहे: https: // www.YouTube.कॉम/वॉच?व्ही = बी-सीओजीएमबीएजी 4

मला आशा आहे की या लेखात आपल्याकडे अधिक आहे आणि सध्याच्या चिप्सच्या निर्मितीबद्दल आपल्याला थोडे अधिक जाणून घेण्याची परवानगी आहे. मी एक जटिल विषय लोकप्रिय करण्याचा प्रयत्न केला, मला आशा आहे की पहिल्या परिच्छेदानंतर मी तुम्हाला ठेवण्यास सक्षम आहे

काही गुण आपल्यासाठी गुप्त राहिल्यास टिप्पणी देण्यास अजिबात संकोच करू नका, मी तपशील प्रदान करण्याचा प्रयत्न करेन.

6 टिप्पण्या

हे उत्तर उपयुक्त होते

उत्कृष्ट लेख, धन्यवाद @ zeql !

“मला लांडग्यांकडे फेकून द्या आणि मी पॅक परत करेन.” – सेनेका

हे उत्तर उपयुक्त होते

मी आश्चर्यचकित होतो की हार्डवेअरमधील विशिष्ट उत्क्रांतीचा विचार करण्यासाठी चपलेट्सचे आगमन किती सक्षम आहे (तसेच ग्राहक-ग्रेड ते सर्व्हर-ग्रेड) भविष्यात किंवा आम्ही संपूर्ण आणि इष्टतम मशीनची रचना ज्या मार्गावर आहे त्यावरील एक प्रतिमान शिफ्ट देखील.

काही चांगल्या समाकलित प्रणाली (विशेषत: Apple पलवर) केवळ अत्यंत कार्यक्षम “क्लासिक” सीपीयूवर आधारित नाहीत, परंतु जनरलिस्ट सीपीयू अनलोड करणार्या अनेक विशिष्ट सहाय्यक चिप्सवर देखील आहेत. स्मार्टफोन म्हणून मर्यादित सिस्टममध्ये, आम्ही एच 265 ट्रान्सकोडिंग चिप्स, एआयसाठी गणना युनिट्स (गणना युनिट्स) शोधू शकतो (Apple पल न्यूरल इंजिन) आणि अर्थातच क्लासिक ग्राफिक युनिट.

म्हणून मी दुसर्या पिढीच्या एएमडी ईपीवायसीचे आकृत्या घेतो आणि मला आश्चर्य वाटते की विशिष्ट कार्यांवर इष्टतम कामगिरी करण्यासाठी अनेक विशिष्ट चिप्स सुरू करणार्या संपूर्ण युनिट्समधून व्यावसायिक आणि औद्योगिकदृष्ट्या व्यवहार्य करण्याचा एक सोपा मार्ग आहे का?. उदाहरणार्थ, एक युनिट क्लासिक सीसीडी प्रदान करू शकेल, परंतु डीएसपी, एक जीपीयू, ट्रान्सको एच 265/एव्ही 1/व्हीपी 9/…, एईएस करण्यासाठी एक चिप इ. आणि हे सर्व आयओडी/अनंत उत्पादनाद्वारे कनेक्ट करा. मशीन/सर्व्हरचे प्रत्येक निर्माता म्हणून स्वत: ची रचना करून आणि आर अँड डी/फॅरामाइनस औद्योगिकीकरण खर्च न करता वापरण्यास तयार अंतिम युनिट तयार करू शकते.

हे मला एपीयूच्या संकल्पनेची आठवण करून देते, परंतु अहवाल आहे की नाही हे मला माहित नाही.

हे उत्तर उपयुक्त होते

मी आश्चर्यचकित होतो की हार्डवेअरमधील विशिष्ट उत्क्रांतीचा विचार करण्यासाठी चपलेट्सचे आगमन किती सक्षम आहे (तसेच ग्राहक-ग्रेड ते सर्व्हर-ग्रेड) भविष्यात किंवा आम्ही संपूर्ण आणि इष्टतम मशीनची रचना ज्या मार्गावर आहे त्यावरील एक प्रतिमान शिफ्ट देखील.

काही चांगल्या समाकलित प्रणाली (विशेषत: Apple पलवर) केवळ अत्यंत कार्यक्षम “क्लासिक” सीपीयूवर आधारित नाहीत, परंतु जनरलिस्ट सीपीयू अनलोड करणार्या अनेक विशिष्ट सहाय्यक चिप्सवर देखील आहेत. स्मार्टफोन म्हणून मर्यादित सिस्टममध्ये, आम्ही एच 265 ट्रान्सकोडिंग चिप्स, एआयसाठी गणना युनिट्स (गणना युनिट्स) शोधू शकतो (Apple पल न्यूरल इंजिन) आणि अर्थातच क्लासिक ग्राफिक युनिट.

म्हणून मी दुसर्या पिढीच्या एएमडी ईपीवायसीचे आकृत्या घेतो आणि मला आश्चर्य वाटते की विशिष्ट कार्यांवर इष्टतम कामगिरी करण्यासाठी अनेक विशिष्ट चिप्स सुरू करणार्या संपूर्ण युनिट्समधून व्यावसायिक आणि औद्योगिकदृष्ट्या व्यवहार्य करण्याचा एक सोपा मार्ग आहे का?. उदाहरणार्थ, एक युनिट क्लासिक सीसीडी प्रदान करू शकेल, परंतु डीएसपी, एक जीपीयू, ट्रान्सको एच 265/एव्ही 1/व्हीपी 9/…, एईएस करण्यासाठी एक चिप इ. आणि हे सर्व आयओडी/अनंत उत्पादनाद्वारे कनेक्ट करा. मशीन/सर्व्हरचे प्रत्येक निर्माता म्हणून स्वत: ची रचना करून आणि आर अँड डी/फॅरामाइनस औद्योगिकीकरण खर्च न करता वापरण्यास तयार अंतिम युनिट तयार करू शकते.

हे मला एपीयूच्या संकल्पनेची आठवण करून देते, परंतु अहवाल आहे की नाही हे मला माहित नाही.

तर आपल्याला हे माहित असले पाहिजे की चिप बर्याचदा आयपी (बौद्धिक संपत्ती) सह केली जाते: “ट्रान्झिस्टर” स्तरावर एक फंक्शन विकले गेले आहे परंतु ते त्याच्या डिझाइनमध्ये समाकलित केले जाणे आवश्यक आहे.

एक क्लासिक उदाहरण म्हणजे डीडीआर 3 कंट्रोलर ऑन -बोर्ड मायक्रोकंट्रोलर. मायक्रोकंट्रोलरची निर्माता डीडीआर 3 वर प्रभुत्व मिळवत नाही आणि त्यात कौशल्य नाही, डीडीआर 3 कंट्रोलर तयार करण्याची वेळ (इच्छा नाही). म्हणूनच तो नियंत्रकाकडून एक आयपी खरेदी करतो आणि त्याला त्याच्या डिझाइनमध्ये समाकलित करतो.

आयपी आणि चिपलेटच्या संभाव्यतेमधील फरक पाहण्यात आपल्याला यशस्वी करावे लागेल. माझ्यासाठी चिपलेट तेथे येऊन एक किंवा अधिक प्रगत वैशिष्ट्ये आणण्यासाठी आहे आणि ज्याने आधीच खोदकामाच्या चाचण्या पार केल्या आहेत, म्हणून डिझाइनमधील एक अतिरिक्त पाऊल. परंतु सर्व चपलेट्ससह संपूर्ण मातीची चाचणी घेण्याची समस्या बाकी आहे. म्हणून आम्ही लेगो सारखे शेकडो भिन्नता तयार करू शकत नाही. हे किमान आर्थिक वास्तव घेते.

पण हो, एका विशिष्ट व्हॉल्यूमसाठी आम्ही à ला कार्टे सॉकेट्स तयार करू शकतो.

मोठा फायदा चिपच्या उत्पादनाच्या बाजूने आहे: जर वेगवेगळ्या खोदकाम बिनधास्तांसाठी एखादा आयपी नाकारला जाऊ शकतो, तर जेव्हा इतर भाग चिप करू शकतात तेव्हा त्याच्या सुरुवातीच्या दंडामध्ये (पुरेसे असल्यास) नेहमीच सक्षम होण्याच्या फायद्याचे एक चिपलेट लहान खोदकाम सह सुधारित व्हा.

हे उत्तर उपयुक्त होते

याशिवाय मी विचार केला की चिपलेट्स मॉड्यूलर डिझाइनमध्ये वापरली जाऊ शकतात. आपण 4 चिप्ससह एक डिझाइन घ्या, दोषांसह पिसू संपूर्ण उत्पादनात वितरित केले जातात आणि 4 वर काम करणार्या 3 चिप्स असलेल्या 4 चिप्स खाली एक श्रेणी असतील आणि 4 काम करण्यापेक्षा थोडी स्वस्त असतील.

जे पारंपारिक ऑपरेशनच्या संबंधात डिझाइन आणि औद्योगिकीकरण सुलभ करते.

विनामूल्य सॉफ्टवेअर आणि जीएनयू/लिनक्स फेडोरा वितरण प्रेमी. #Jesuisaris

हे उत्तर उपयुक्त होते

या मनोरंजक मेगा लेखाबद्दल धन्यवाद. प्रत्येक बिंदूचे तपशीलवार वर्णन करण्यासाठी मला तुमच्यावर खूप प्रेम आहे की आपण खरोखर गोष्टी समजून घेण्यासाठी ट्यूटोरियलमध्ये स्पष्टीकरण देत नाही परंतु तरीही मनोरंजक आहे .

3 डी आयसी विषम एकत्रीकरणासाठी मार्ग मोकळा करण्यासाठी चिपलेट डिझाइन किट वापरणे

एक चिपलेट एक एएसआयसी डाय विशिष्टरित्या डिझाइन केलेले आहे आणि इतर चिपलेट्सच्या संयोगाने पॅकेजमध्ये ऑपरेशनसाठी ऑप्टिमाइझ केलेले आहे. हेटरोजेनियस इंटिग्रेटेड (एचआय) मध्ये सिस्टम-इन-पॅकेज (एसआयपी) चिपलेट्समध्ये इंडिव्हेंट मल्टीपल डाय किंवा चिपलेट्सचा समावेश आहे. या उपकरणांमध्ये अनुशासनात्मक फायदे, समाविष्ट कामगिरी, शक्ती, क्षेत्र, किंमत आणि टीटीएम म्हणून ऑफर केली गेली.

चिपलेट डिझाईन एक्सचेंज (सीडीएक्स) मध्ये ईडीए विक्रेते, चिपलेट असतात

प्रदाता/असेंबलर्स आणि एसआयपी इंटिग्रेटर आणि चिपलेट इकोसिस्टम सुलभ करण्यासाठी प्रमाणित चिपलेट मॉडेल आणि वर्कफ्लोची शिफारस करण्यासाठी एक मुक्त कार्य गट आहे. हे वेबिनार चिपलेट डिझाइन किट्स (सीडीके) चे प्रमाणित करण्यात मदत करण्यासाठी ऑफर करते 2.5 डी आणि 3.ओपन इकोसिस्टम तयार करण्यासाठी डी आयसी डिझाइन.

यशस्वी 2 साठी इकोसिस्टम तयार करणे.5 डी आणि 3 डी चिपलेट मॉडेल एकत्रीकरण

एसओसी प्रक्रियेप्रमाणेच, आपल्याला चिपलेट्ससाठी एक इकोसिस्टम आवश्यक आहे. सामान्य बाजारपेठेतील दत्तक आणि चिपलेट आधारित डिझाइनच्या तैनातीसाठी की सक्षम करते:

- तंत्रज्ञान: 2.5 डी इंटरपोजिशन आणि 3 डी स्टॅक केलेले डाय मॅन्युफॅक्चरिंग आणि असेंब्ली प्रक्रिया

- आयपी: प्रमाणित चिपलेट मॉडेल

- वर्कफ्लो: ईडीए डिझाइन प्रवाह आणि पीडीके, सीडीके, डीआरएम आणि असेंब्ली नियम

- व्यवसाय मॉडेल: चिपलेट मार्केटप्लेस

सीडीएक्सचे प्रारंभिक फोकस 2 आहे.अनुसरण करण्यासाठी 3 डी सह 5 डी इंटरपोजिंग-आधारित चिपलेट मॉडेल. वेबिनारमध्ये या प्रयत्नांबद्दल अधिक जाणून घ्या.

चिपलेट डिझाईन एक्सचेंज (सीडीएक्स) मध्ये ईडीए विक्रेते, चिपलेट प्रदाता/असेंबलर्स आणि एसआयपी इंटिग्रेटर असतात आणि चिपलेट इकोसिस्टम सुलभ करण्यासाठी प्रमाणित चिपलेट मॉडेल आणि वर्कफ्लोची शिफारस करण्यासाठी एक मुक्त कार्य गट आहे. हे वेबिनार चिपलेट डिझाइन किट्स (सीडीके) चे प्रमाणित करण्यात मदत करण्यासाठी ऑफर करते 2.5 डी आणि 3.ओपन इकोसिस्टम तयार करण्यासाठी डी आयसी डिझाइन.

यशस्वी 2 साठी इकोसिस्टम तयार करणे.5 डी आणि 3 डी चिपलेट मॉडेल एकत्रीकरण

एसओसी प्रक्रियेप्रमाणेच, आपल्याला चिपलेट्ससाठी एक इकोसिस्टम आवश्यक आहे. सामान्य बाजारपेठेतील दत्तक आणि चिपलेट आधारित डिझाइनच्या तैनातीसाठी की सक्षम करते:

- तंत्रज्ञान: 2.5 डी इंटरपोजिशन आणि 3 डी स्टॅक केलेले डाय मॅन्युफॅक्चरिंग आणि असेंब्ली प्रक्रिया

- आयपी: प्रमाणित चिपलेट मॉडेल

- वर्कफ्लो: ईडीए डिझाइन प्रवाह आणि पीडीके, सीडीके, डीआरएम आणि असेंब्ली नियम

- व्यवसाय मॉडेल: चिपलेट मार्केटप्लेस

सीडीएक्सचे प्रारंभिक फोकस 2 आहे.अनुसरण करण्यासाठी 3 डी सह 5 डी इंटरपोजिंग-आधारित चिपलेट मॉडेल. वेबिनारमध्ये या प्रयत्नांबद्दल अधिक जाणून घ्या.

लीक केलेल्या प्रतिमेत जीपीयू एएमडी रॅडियनसाठी चिपलेटची महत्वाकांक्षी रचना दिसून येते

लीक केलेल्या प्रतिमेत जीपीयू एएमडी रॅडियनसाठी चिपलेटची महत्वाकांक्षी रचना दिसून येते

- द्वारा

- बातम्यांमध्ये

- 16 ऑगस्ट 2023 रोजी

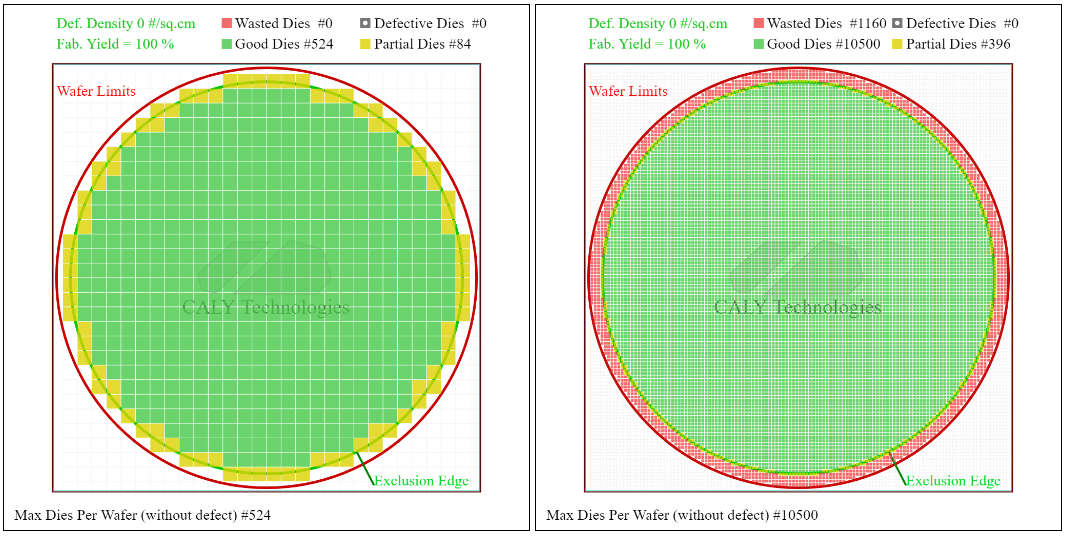

एक लीक केलेली प्रतिमा समोर आली आहे, ज्यात रॅडियन चिपलेट्ससह जीपीयू डिझाइन उघडकीस आले आहे, असे मानले जाते की नवी 4 सी चिप 4 सी च्या रद्द केलेल्या प्रकल्पातून. महत्वाकांक्षी एएमडी पध्दतीची साक्ष देणारी एकाच जीपीयूवर 13 ते 20 वेगवेगळ्या चिपलेट्स दरम्यानची रचना. हे अधिक जटिल चिपलेट डिझाइन सध्या रॅडियन आरएक्स 7900 एक्सटीएक्समध्ये वापरल्या जाणार्या नवी 31 सिलिकॉनपेक्षा भिन्न आहे. जीपीयूच्या मागील पुनरावृत्तीला प्रथम पिढी मानली जात होती, परंतु एएमडीच्या अलीकडील रायझन प्रोसेसर सारख्या वास्तविक चिपलेट डिझाइनचा वापर केला नाही. तथापि, नवी 4 सी ची संकल्पना एक महत्त्वपूर्ण आगाऊ प्रतिनिधित्व करते, कारण त्यात एकाच सब्सट्रेटवर अनेक गणना चिपल, तसेच वेगळ्या आय/ओ चपलेट्सचा समावेश आहे. लीक केलेली प्रतिमा 13 चिप्सेट्स सादर करते, अतिरिक्त मेमरी कंट्रोलर चिप्सच्या प्रतिमेवर प्रदर्शित होत नाही.

प्रतिमेच्या सत्यतेची पुष्टी करण्यासाठी, समांतर प्रोसेसरमधील मॉड्यूलरिटीच्या संकल्पनेवर चर्चा करणारे 2021 चे संबंधित पेटंट हायलाइट केले आहे. पेटंटचे नमुने लीक केलेल्या प्रतिमेमध्ये दर्शविलेल्या डिझाइनशी जवळून साम्य आहेत, अगदी ट्रान्सव्हर्स कपच्या दुसर्या बाजूला अधिक चपळांची शक्यता देखील सूचित करते.

दुर्दैवाने, लीक झालेल्या प्रतिमेमध्ये सादर केलेल्या जीपीयूच्या डिझाइन रद्द केले गेले आहे. हे अलीकडील संबंधांशी सहमत आहे की जीपीयूच्या पुढच्या पिढीसाठी एएमडीचा उच्चारण उच्च -एंड घटकांऐवजी सामान्य लोकांसाठी नवी 43 आणि नवी 44 मोनोलिथिक चिप्सवर असेल. तथापि, असा अंदाज लावला जात आहे की एएमडी त्याच्या भविष्यातील ग्राफिक्स कार्डच्या उच्च -एंड सेगमेंटसाठी अनेक गणना चिपलेट्सच्या जीपीयूच्या विकासासाठी आपले प्रयत्न पुनर्निर्देशित करते, संभाव्यत: आरडीएनए 5 सह संभाव्यत: आरडीएनए 5 सह.

पारंपारिक सीपीयू गणनांपेक्षा गेम ग्राफिक्ससाठी अनेक गणना चिपलेट्सची जाणीव अधिक जटिल असली तरीही, एएमडीने आता डिझाइन अडथळ्यांवर मात करण्याचा निर्णय घेतला आणि आरडीएनए 5 साठी अधिक चांगल्या समाधानावर कार्य केले आहे. एएमडीला बचाव योजना असणे फायदेशीर ठरले असते, जसे नवी 31 च्या सुधारित आवृत्तीसाठी नवीन नोड.