Kemunculan Chiplets • Artikel • Zest of Knowledge, Kit Reka Bentuk Chiplet untuk Integrasi Heterogen 3D | Perisian Siemens

Menggunakan kit reka bentuk chiplet untuk membantu membuka jalan untuk integrasi heterogen 3D

Contents

- 1 Menggunakan kit reka bentuk chiplet untuk membantu membuka jalan untuk integrasi heterogen 3D

- 1.1 Kedatangan chiplet

- 1.2 Mukadimah

- 1.3 Chiplet, Quésaco ?

- 1.4 Aspek ekonomi chiplet

- 1.5 Dua contoh: AMD dan Intel (Altel)

- 1.6 Menggunakan kit reka bentuk chiplet untuk membantu membuka jalan untuk integrasi heterogen 3D

- 1.7 Membina ekosistem untuk berjaya 2.Integrasi Model Chiplet 5D dan 3D

- 1.8 Membina ekosistem untuk berjaya 2.Integrasi Model Chiplet 5D dan 3D

- 1.9 Imej bocor mendedahkan reka bentuk chiplet yang bercita -cita tinggi untuk GPU AMD Radeon

- 1.10 Imej bocor mendedahkan reka bentuk chiplet yang bercita -cita tinggi untuk GPU AMD Radeon

Beberapa tahun kemudian, pemproses pertama muncul dengan khususnya Intel 4004, agak mudah hari ini. Maka pemproses menjadi lebih kompleks.

Kedatangan chiplet

Berikutan perbincangan di JZD dan pada perselisihan, saya memberitahu diri saya bahawa menulis artikel mengenai chiplets akan memberi manfaat kepada jumlah yang paling besar. Dan akan mengekalkan jejak bertulis yang bertentangan dengan apa yang boleh berlaku kepada JZD

Daripada menulis tiket yang sangat panjang, saya lebih suka format artikel untuk mendapatkan sedikit lagi ke dalam butiran. Saya berharap dapat mengajar anda apa chiplets, mengapa teknologi ini dicipta dan mengapa ia akan berkembang pada tahun -tahun yang akan datang.

- Mukadimah

- Chiplet, Quésaco ?

- Aspek ekonomi chiplet

- Dua contoh: AMD dan Intel (Altel)

Mukadimah

Artikel ini bercakap mengenai konsep komputer, elektronik dan seni bina komputer yang boleh cukup maju untuk pembaca tertentu. Saya menawarkan sedikit populalisasi dalam mukadimah ini untuk memahami sedikit lebih baik apa yang kita bicarakan.

Bagi pemurni, pintasan akan dibuat, populasi ini mungkin dapat mengandungi maklumat yang tidak tepat secara sukarela untuk memudahkan pemahaman.

Chiplet, Quésaco ?

Mari kita mulakan dengan yang paling sukar, tentukan apa itu chiplet !

Sesungguhnya istilah chiplet muncul pada tahun 1970 -an tetapi penggunaannya telah dimatikan pada tahun -tahun kebelakangan ini, bagi mereka yang berminat dengan pemproses kompleks atau cip elektronik seperti FPGA (cip yang pintu logik dalamannya boleh diprogramkan semula). Bagi yang lain, di bahagian bawah bilik, anda mungkin tidak pernah mendengar istilah ini, kami akan membetulkannya !

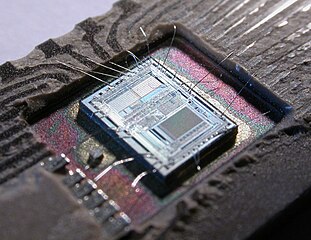

Mari kita kembali ke dasar cip elektronik: sekeping silikon terukir (transistor terkenal) yang terkandung dalam kes. Dengan komponen persimpangan, benang emas atau perak kecil menyambungkan kaki komponen ke sekeping silikon. Pada mulanya, cip itu terdiri daripada transistor yang terukir dengan resolusi yang agak kasar (berbanding hari ini) dan fungsi -fungsi itu agak asas: pintu logik, penguat operasi, dll. Walau bagaimanapun, ia sudah menjadi kemajuan besar dari segi pengurangan !

Pada masa itu komponen mempunyai kaki menyeberang dan perlu menyambungkan cip silikon ke kaki ini. Ia dibuat dengan anak -anak nipis perak atau emas yang dikimpal di antara cip dan kaki di dalam kes itu.

Beberapa tahun kemudian, pemproses pertama muncul dengan khususnya Intel 4004, agak mudah hari ini. Maka pemproses menjadi lebih kompleks.

Dari tahun 1970 -an, IBM membangunkan komponen MCM (Multi-chodu) termasuk beberapa cip silikon dalam satu kes. Tetapi teknologi ini akan berkembang pada akhir 90 -an. Kita dapat perhatikan Pentium Pro Intel yang dikeluarkan pada tahun 1995. Pemproses ini termasuk dua cip silikon: satu untuk pemproses dengan tegas dan satu lagi untuk memori cache L2 (memori penampan antara pemproses dan RAM, jauh lebih cepat tetapi lebih mahal kerana terukir dengan pemproses).

Seperti yang dapat kita lihat dalam foto, kedua -dua cip mempunyai saiz yang sama dan Intel menawarkan beberapa saiz cache L2. Kelebihan memisahkan pemproses memori cache adalah untuk dapat menyimpan skala pada cip pemproses sambil menawarkan saiz memori cache yang berbeza dengan meletakkan cip saiz yang berbeza dalam kes itu.

Komponen jenis ini kekal kurang berkembang, walaupun IBM terus membangunkan komponen MCM. Perhatikan Power5 IBM yang dikeluarkan pada tahun 2004 yang melihat empat pemproses tepat dengan cip memori cache L3. Sambungan kutu dilakukan di dalam kes itu.

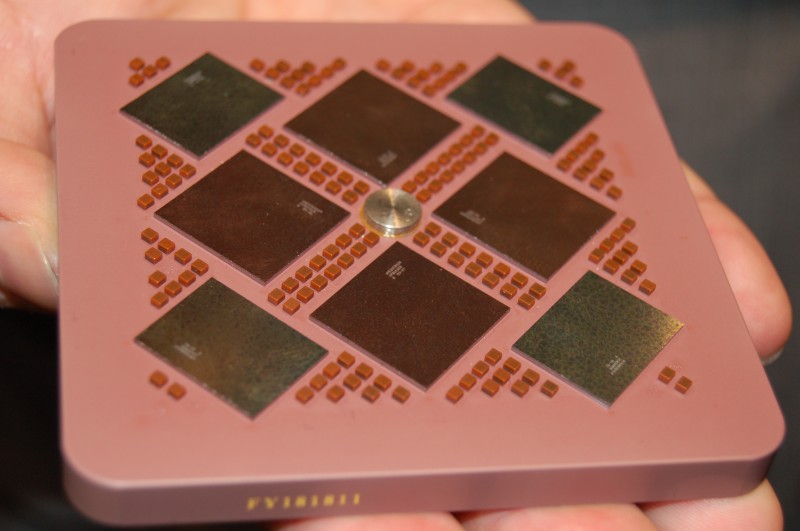

Hari ini teknologi telah berkembang dan cip MCM hadir dalam produk pengguna dengan pemproses AMD. Di sini kita dapat melihat pemproses EPYC 7702 (dikeluarkan pada bulan Ogos 2019) yang terdiri daripada 9 cip silikon yang saling berkaitan: 8 cip yang mengandungi teras dan memori cache dan cip pusat yang menghubungkan 8 yang lain dan yang menguruskan DDR serta isyarat D ‘ Keluar (SATA, PCI Express, USB, dll.))).

Tetapi beritahu saya Jamy, apa itu chiplet ?

Ah ya, saya mendapat sedikit

Malah chiplet adalah salah satu cip silikon yang terdapat di MCM. Chiplet dibuat untuk saling berkaitan dengan chiplet lain. Ya agak mudah tetapi anda terpaksa menunjukkan beberapa gambar yang bagus untuk difahami

Walau bagaimanapun, sedikit lebih tepat mengenai makna chiplets, idea itu tidak semestinya untuk meletakkan beberapa cip yang berbeza yang dihubungkan bersama. Terdapat juga tanggapan cip generik yang boleh digunakan semula dan tidak didedikasikan untuk rujukan pemproses tertentu.

Aspek ekonomi chiplet

Selepas pengenalan ini semasa imej, mari kita faham mengapa chiplet akan berkembang pada masa akan datang. Untuk melakukan ini, perlu kembali ke proses pembuatan kutu elektronik.

Duduk dengan selesa di kerusi berlengan kerana perjalanan dari pantai berpasir akan lama

Tidak, tunggu !

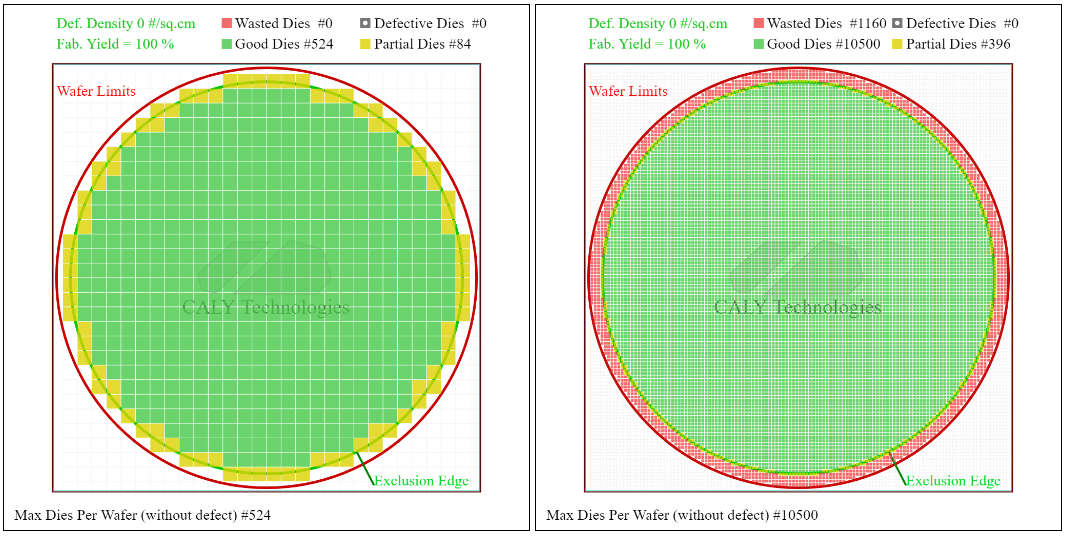

Kami akan menghabiskan seluruh bahagian pembuatan silikon. Apa yang akan menarik minat kita ialah pengedaran kutu (mati) pada kek silikon (wafer) dan khususnya evolusi hasil dengan peningkatan dalam ukiran ukiran.

Tetapi sebelum aspek hasil ini, kita mesti bercakap mengenai saiz fizikal maksimum mati. Sesungguhnya, pada pancake silikon reka bentuk yang sama cip diulang beberapa kali (puluhan atau bahkan seratus kali). Kesan reka bentuk ini dilakukan secara optik melalui cahaya ultraviolet. Walau bagaimanapun terdapat satu set keseluruhan kanta dan mekanisme optik yang menghalang ukiran satu mati pada seluruh kek silikon.

Semakin kita merumitkan kutu, semakin kita mahu meletakkan transistor, jadi kita mesti meningkatkan saiz cip, atau meningkatkan makanan ukiran agar sesuai dengan lebih banyak transistor di permukaan yang sama. Tetapi ada kekangan dan had lain yang dirasakan.

Inilah sebabnya mengapa prinsip chiplet menarik untuk memintas had ini: Gunakan beberapa cip silikum kecil yang disambungkan bersama untuk membuat cip yang lebih kompleks tetapi mustahil untuk mengukir dengan cara monolitik.

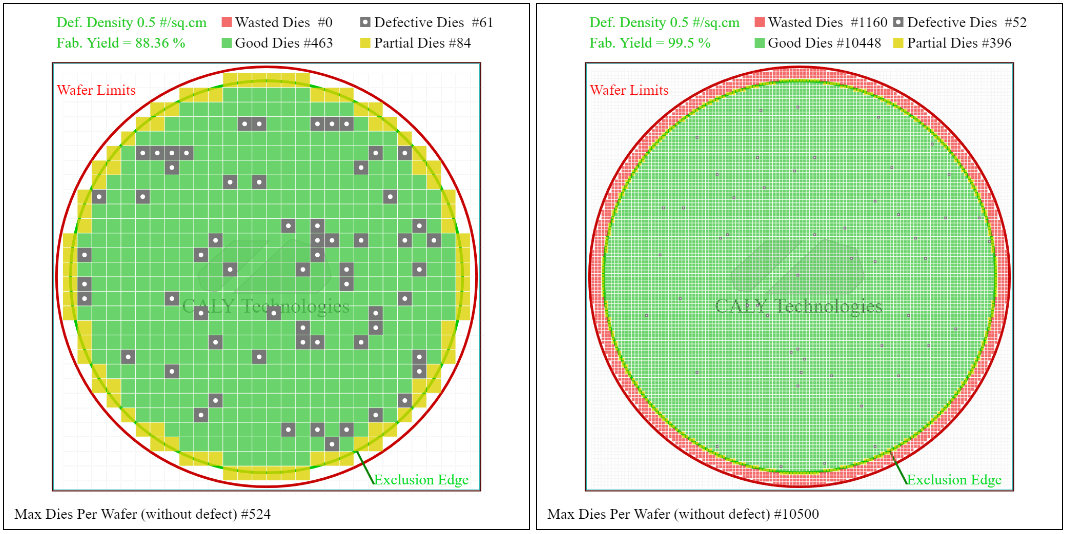

Sekarang kembali ke hasil (hasil dalam Bahasa Inggeris). Pertama, wafer berbentuk bulat dan kami mahu mengukirnya dengan kerepek segi empat tepat. Keseluruhan silikon tidak digunakan. Tetapi semakin kecil mati di tepi dan semakin kita dapat mati secara keseluruhan. Ini adalah prinsip yang sama seperti aliasing dalam permainan video: semakin banyak piksel yang digunakan untuk membentuk bentuk bulat yang kecil dan semakin kurang kita menyedari.

Dalam contoh di atas, jika kita melaporkan separa mati pada jumlah yang mati (baik dan berat sebelah) kita memperoleh nisbah 13.8 % dalam kes mati 5 × 5 mm dan 3.6 % dalam kes 1 × 1 mm mati. Semakin kecil mati, yang lebih sah mati di tepi, yang meningkatkan hasil.

Anda juga boleh membuat campuran mati yang besar di tengah wafer dan menggunakan mati yang lebih kecil di tepi untuk mengoptimumkan hasil kerana aliasing.

Katakan Jamy, mengapa kita menggunakan wafer bulat untuk membuat kutu segi empat tepat ?

Baik itu kerana kaedah membuat silikon yang dipanggil proses czochralski yang memberikan silikon dalam bentuk silinder, dipotong menjadi irisan yang sangat halus untuk memberi wafer.

Kedua, hasilnya dipengaruhi oleh kecacatan yang mungkin muncul di wafer. Anda boleh memikirkan bijirin habuk yang jatuh di wafer.

Saya meneruskan contoh sebelumnya dengan menambahkan ketumpatan kesalahan 0.5 per cm². Sekarang bandingkan Menghasilkan pembuatan yang sepadan dengan nisbah antara bilangan fungsi mati dan jumlah produk yang dihasilkan. Dalam kes mati 5 × 5 mm, hasilnya adalah 88.4 % manakala dengan 1 × 1 mm mati, hasilnya 99.5 %.

Oleh itu, adalah dua kali ganda menarik untuk mati kecil untuk mengoptimumkan pengeluaran kutu elektronik. Walau bagaimanapun, memotong cip kompleks ke dalam beberapa cip yang lebih kecil memerlukan menyampaikan cip yang berbeza di antara mereka, oleh itu kita mesti menambah elemen komunikasi yang datang untuk mengambil ruang tambahan dan menggunakan tenaga tambahan.

Di samping itu, penggunaan chiplets boleh memungkinkan untuk menggunakan kematian ukiran yang berbeza mengikut fungsi yang membolehkan memodulasi kos cip akhir dengan prestasi.

Akhirnya, satu lagi aspek ekonomi yang dapat dilihat ialah kerumitan membangunkan ciri -ciri baru. Ini cenderung mempunyai syarikat khusus (atau sekurang-kurangnya permulaan pada permulaan) yang menawarkan blok harta intelek (fungsi) siap digunakan. Sebagai contoh, pengeluar pemproses akan dapat memberi tumpuan kepada pembangunan pemproses itu sendiri semasa membeli mati untuk fungsi seperti PCI Express, USB atau DDR pengawal.

Untuk memudahkan kebolehoperasian chiplet yang datang dari pengeluar yang berbeza, pemain utama seperti Intel, AMD, ARM, Qualcomm, Samsung atau TSMC telah mencipta standard komunikasi antara cipplets, UCIE (Universal chiplet interconnect express))).

Dua contoh: AMD dan Intel (Altel)

AMD EPYC

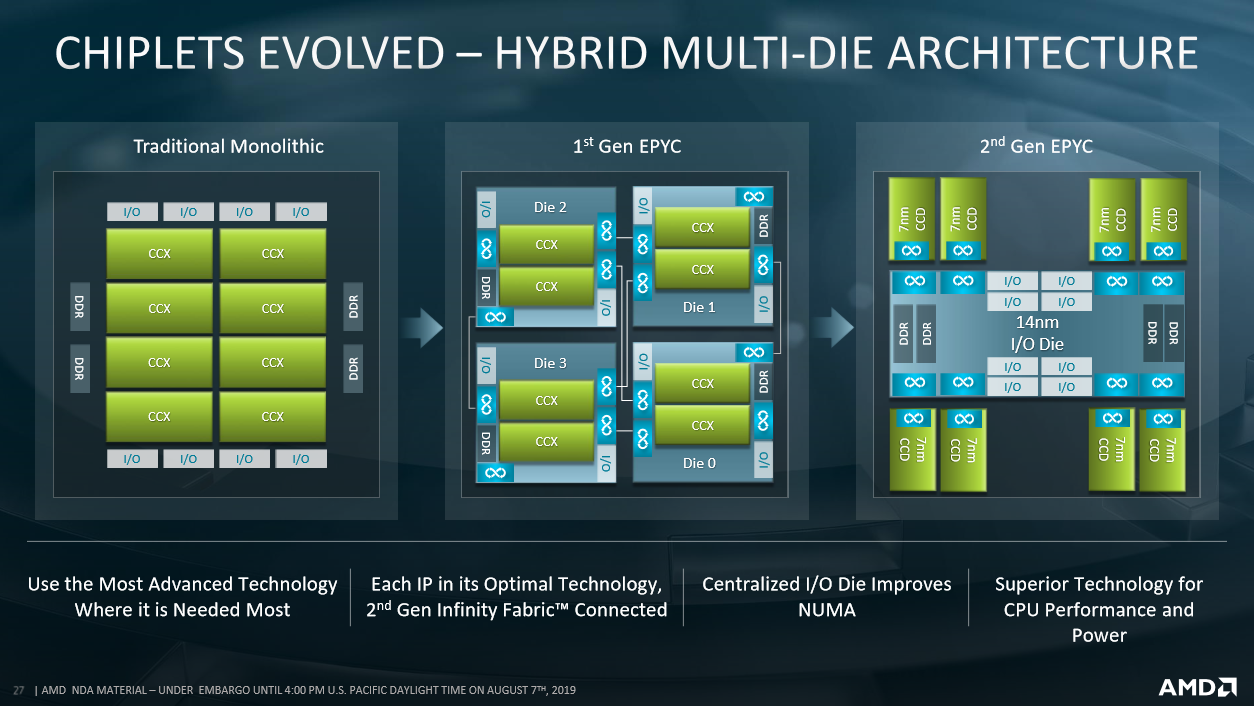

Hari ini semakin banyak pemproses menggunakan teknik chiplets ini. AMD menggunakan chiplets sejak generasi pertama pemproses EPYC, di mana hati yang berbeza dihubungkan bersama olehKain infiniti.

Generasi pertama pemproses EPYC menyaksikan satu set mati yang dapat disamakan dengan pemproses lengkap yang dihubungkan bersama olehKain infiniti Untuk membentuk pemproses akhir. Oleh itu, chiplets adalah semacam pemproses autonomi kecil: masing -masing mati menguruskan penyertaan/outputnya dan mempunyai pengawal DDRnya.

Ini mati, atau sebaliknya chiples, mempunyai dua Kompleks pengiraan teras (CCX, satu set empat teras dengan memori cache) serta pengawal DDR, menguruskan input/output (PCI Express misalnya) dan mempunyai modul komunikasi untukKain infiniti.

Kehalusan kecil, selalu ada empat chiplets pada EPYC generasi pertama. Untuk mengubah jumlah hati, amd menyahaktifkan hati di dalam CCX. Contohnya mempunyai 24 teras, CCX hanya mempunyai 3 teras aktif

Oleh itu, generasi pertama ini menggunakan prinsip chiplets sebagai sejenis salinan/terpaku mati dan bukannya membangunkan mati monolitik yang besar.

Untuk generasi kedua, AMD menolak konsepnya sedikit lebih jauh. Malah, CCX kini bebas, dikelompokkan secara berpasangan dalam a Teras mengira mati (CCD) dihubungkan oleh Kain infiniti kepada mati menguruskan DDR dan penyertaan/keluar yang dipanggil Saya/o mati (Iod).

AMD mengeksploitasi sepenuhnya pemisahan ini dari fungsi. Memang CCD diukir dalam 7 nm manakala IOD diukir dalam 14 nm.

Di bawah persembahan AMD meringkaskan laluan dalam chiplets pemproses EPYC.

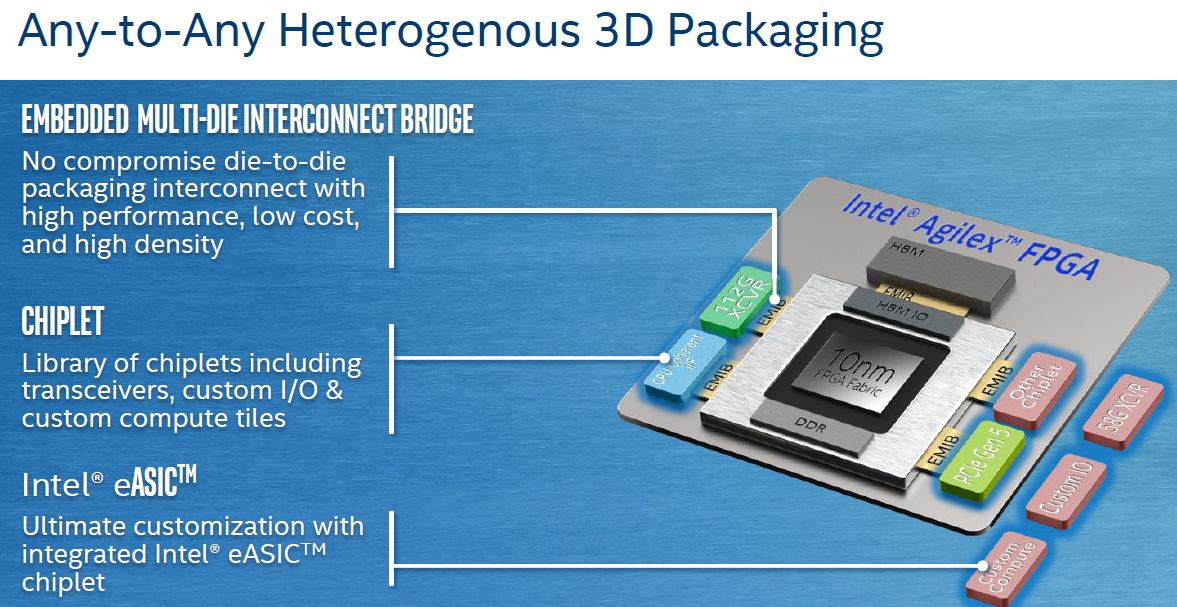

Intel FPGA (Altera)

Pemproses Intel selalu cip monolitik kecuali beberapa pengecualian seperti yang dapat kita lihat pada permulaan artikel ini. Walau bagaimanapun dalam sektor Intel FPGA (FPGA yang boleh dikonfigurasikan) menggunakan chiples untuk generasi terkini, Agilex.

Chiplets ini terutamanya membimbangkan jenis transcense yang digunakan (pautan cepat) dan dipanggil Jubin. Sekiranya Intel menawarkan julat yang telah ditetapkan dari jubin ini, mesti ada cip yang disesuaikan untuk keperluan anda sendiri.

Jubin dibahagikan dengan kelajuan maksimum transceiver dan protokol yang disokong (Ethernet, PCI Express, dll.): 16g untuk p, 28g untuk h, 32g untuk r, dll.

Intel juga membangkitkan masa depan kemungkinan menghubungkan chiples disesuaikan yang akan memberikan fungsi tambahan. Pada masa ini syarikat telah mengeluarkan chiplet ADC/DAC (Jariett Technologies) serta satu lagi sambungan optik (Ayar Labs).

Akhirnya kita tidak boleh mempercayai sama ada kerepek Monolitik sudah mati. Mereka sentiasa mempunyai kelebihan, terutamanya dari segi komunikasi dalaman dan latensi, yang boleh menjadi kritikal untuk aplikasi tertentu yang memerlukan kerepek besar -besaran.

Ini adalah kes Broadcom dan cip suis 400g yang pilihannya dijelaskan oleh pereka dalam video ini: https: // www.Youtube.Com/watch?V = B-COGMBAUG4

Saya harap artikel ini lebih banyak untuk anda dan membolehkan anda mengetahui lebih lanjut mengenai pembuatan cip semasa. Saya cuba mempopularkan subjek yang kompleks, saya juga berharap saya dapat menjaga anda selepas perenggan pertama

Jangan teragak -agak untuk meninggalkan komen jika titik tertentu tetap samar untuk anda, saya akan cuba memberikan butiran.

6 komen

Jawapan ini berguna

Artikel yang sangat baik, terima kasih @ zeql !

“Buang saya ke serigala dan saya akan mengembalikan pek.” – Seneca

Jawapan ini berguna

Saya tertanya -tanya berapa banyak kemunculan chiplet yang dapat mempertimbangkan evolusi tertentu dalam perkakasan (juga gred pengguna itu gred pelayan) pada masa akan datang, atau bahkan paradigma beralih dengan cara kami merancang mesin yang sangat dan optimum secara keseluruhan.

Sistem bersepadu tertentu (terutamanya di Apple) tidak berdasarkan semata -mata pada CPU “klasik” yang sangat berkesan, tetapi juga pada beberapa cip tambahan khusus yang memunggah CPU generalis. Dalam sistem yang terhad sebagai telefon pintar, kami dapat menemui cip transcoding H265, unit pengiraan untuk AI (Enjin saraf epal) dan tentu saja unit grafik klasik.

Oleh itu, saya mengambil gambarajah AMD EPYC generasi ke -2 dan saya tertanya -tanya jika chiplets akan menjadi cara mudah untuk menghasilkan secara komersil dan industri yang berdaya maju dari unit lengkap yang memulakan beberapa cip khusus untuk mencapai prestasi yang optimum pada tugas -tugas tertentu. Sebagai contoh, unit boleh menyediakan untuk CCD klasik, tetapi juga DSP, GPU, Transco H265/AV1/VP9/…, cip untuk melakukan AES, dll. dan sambungkan semuanya melalui pembuatan IOD/Infinity. Oleh itu, setiap pengeluar mesin/pelayan dapat menyusun unit akhir yang siap digunakannya dengan membentuk sendiri dan tanpa kos perindustrian R & D/Faramineurous.

Ini mengingatkan saya tentang konsep APU, tetapi saya tidak tahu jika ada laporan.

Jawapan ini berguna

Saya tertanya -tanya berapa banyak kemunculan chiplet yang dapat mempertimbangkan evolusi tertentu dalam perkakasan (juga gred pengguna itu gred pelayan) pada masa akan datang, atau bahkan paradigma beralih dengan cara kami merancang mesin yang sangat dan optimum secara keseluruhan.

Sistem bersepadu tertentu (terutamanya di Apple) tidak berdasarkan semata -mata pada CPU “klasik” yang sangat berkesan, tetapi juga pada beberapa cip tambahan khusus yang memunggah CPU generalis. Dalam sistem yang terhad sebagai telefon pintar, kami dapat menemui cip transcoding H265, unit pengiraan untuk AI (Enjin saraf epal) dan tentu saja unit grafik klasik.

Oleh itu, saya mengambil gambarajah AMD EPYC generasi ke -2 dan saya tertanya -tanya jika chiplets akan menjadi cara mudah untuk menghasilkan secara komersil dan industri yang berdaya maju dari unit lengkap yang memulakan beberapa cip khusus untuk mencapai prestasi yang optimum pada tugas -tugas tertentu. Sebagai contoh, unit boleh menyediakan untuk CCD klasik, tetapi juga DSP, GPU, Transco H265/AV1/VP9/…, cip untuk melakukan AES, dll. dan sambungkan semuanya melalui pembuatan IOD/Infinity. Oleh itu, setiap pengeluar mesin/pelayan dapat menyusun unit akhir yang siap digunakannya dengan membentuk sendiri dan tanpa kos perindustrian R & D/Faramineurous.

Ini mengingatkan saya tentang konsep APU, tetapi saya tidak tahu jika ada laporan.

Oleh itu, anda harus tahu bahawa cip sering dilakukan dengan IP (harta intelektual): Fungsi yang dijual cukup siap pada tahap “transistor” tetapi itu mesti diintegrasikan ke dalam reka bentuknya.

Contoh klasik adalah pengawal DDR3 pada mikrokontroler papan pada. Pengilang mikrokontroler tidak semestinya menguasai DDR3 dan tidak mempunyai kemahiran, masa (tidak keinginan) untuk membuat pengawal DDR3. Oleh itu, dia membeli IP dari pengawal dan mengintegrasikannya ke dalam reka bentuknya.

Anda mesti berjaya melihat perbezaan antara kemungkinan IP dan chiplet. Bagi saya chiplet ada di sana untuk datang dan membawa satu atau lebih ciri -ciri canggih dan yang telah lulus ujian ukiran, oleh itu langkah tambahan dalam reka bentuk. Tetapi masih ada masalah untuk menguji tanah penuh dengan semua chiplet. Oleh itu, kita tidak dapat mencipta beratus -ratus variasi seperti lego. Memerlukan realiti ekonomi yang minimum.

Tetapi ya, untuk jumlah tertentu kita boleh membuat soket à la carte.

Kelebihan besar adalah di bahagian pengeluaran cip: jika IP boleh ditolak untuk kemahiran ukiran yang berbeza, chiplet untuk kelebihan dapat sentiasa diukir dalam kemahiran awalnya (jika ia mencukupi) apabila bahagian lain cip boleh diperbaiki dengan ukiran yang lebih kecil.

Jawapan ini berguna

Selain itu saya fikir bahawa chiplet boleh digunakan dalam reka bentuk modular. Anda mengambil reka bentuk dengan 4 cip, kutu dengan kesalahan diedarkan sepanjang pengeluaran, dan mereka yang mempunyai 3 cip yang berfungsi pada 4 akan menjadi jarak di bawah dan sedikit lebih murah daripada mereka yang mempunyai 4 yang bekerja.

Yang memudahkan reka bentuk dan perindustrian berhubung dengan operasi konvensional.

Kekasih Perisian Percuma dan Pengedaran Fedora GNU/Linux. #Jesuisarius

Jawapan ini berguna

Terima kasih atas artikel mega yang menarik ini. Saya akan mengasihi anda terlalu banyak masa untuk terperinci setiap titik yang anda tidak jelaskan dalam tutorial untuk benar -benar memahami perkara tetapi menarik .

Menggunakan kit reka bentuk chiplet untuk membantu membuka jalan untuk integrasi heterogen 3D

Chiplet adalah mati ASIC yang direka bentuk dan dioptimumkan khusus untuk operasi dalam pakej bersempena dengan chiples lain. Heterogen Bersepadu (HI) melibatkan pelbagai cip atau chiplets ke dalam sistem dalam pakej (SIP). Peranti ini ditawarkan untuk menjadi faedah yang konsisten, termasuk prestasi, kuasa, kawasan, kos dan TTM.

Pertukaran Reka Bentuk Chiplet (CDX) terdiri daripada Vendor EDA, Chiplet

Penyedia/pemasang dan penyepadu SIP dan merupakan kumpulan kerja terbuka untuk mengesyorkan model chiplet dan aliran kerja yang standard untuk memudahkan ekosistem chiplet. Webinar ini meringkaskan kit reka bentuk chiplet (CDK) yang ditawarkan untuk membantu menyeragamkan 2.5d dan 3.Reka bentuk d ic untuk mewujudkan ekosistem terbuka.

Membina ekosistem untuk berjaya 2.Integrasi Model Chiplet 5D dan 3D

Sama dengan proses SOC, anda memerlukan ekosistem untuk cipplets. Kunci membolehkan penggunaan pasaran umum dan penggunaan reka bentuk berasaskan chiplet termasuk:

- Teknologi: 2.5 D Interposition dan 3D disusun proses pembuatan dan pemasangan mati

- IP: Model chiplet standard

- Aliran Kerja: Aliran Reka Bentuk EDA dan Peraturan PDK, CDK, DRM & Perhimpunan

- Model Perniagaan: Chiplet Marketplace

Tumpuan awal CDX ialah 2.Model chiplet berasaskan 5D dengan 3D untuk mengikuti. Ketahui lebih lanjut mengenai usaha ini dalam webinar.

Pertukaran Reka Bentuk Chiplet (CDX) terdiri daripada vendor EDA, penyedia chiplet/pemasak dan penyepadu SIP dan merupakan kumpulan kerja terbuka untuk mengesyorkan model chiplet dan aliran kerja yang standard untuk memudahkan ekosistem chiplet. Webinar ini meringkaskan kit reka bentuk chiplet (CDK) yang ditawarkan untuk membantu menyeragamkan 2.5d dan 3.Reka bentuk d ic untuk mewujudkan ekosistem terbuka.

Membina ekosistem untuk berjaya 2.Integrasi Model Chiplet 5D dan 3D

Sama dengan proses SOC, anda memerlukan ekosistem untuk cipplets. Kunci membolehkan penggunaan pasaran umum dan penggunaan reka bentuk berasaskan chiplet termasuk:

- Teknologi: 2.5 D Interposition dan 3D disusun proses pembuatan dan pemasangan mati

- IP: Model chiplet standard

- Aliran Kerja: Aliran Reka Bentuk EDA dan Peraturan PDK, CDK, DRM & Perhimpunan

- Model Perniagaan: Chiplet Marketplace

Tumpuan awal CDX ialah 2.Model chiplet berasaskan 5D dengan 3D untuk mengikuti. Ketahui lebih lanjut mengenai usaha ini dalam webinar.

Imej bocor mendedahkan reka bentuk chiplet yang bercita -cita tinggi untuk GPU AMD Radeon

Imej bocor mendedahkan reka bentuk chiplet yang bercita -cita tinggi untuk GPU AMD Radeon

- oleh

- Dalam berita

- pada 16 Ogos 2023

Imej yang bocor telah muncul, mendedahkan reka bentuk GPU dengan chiples radeon, yang kononnya dari projek yang dibatalkan dari navi 4c cip 4c. Reka bentuk yang hadir di antara 13 dan 20 chiplet yang berbeza pada GPU tunggal, memberi keterangan kepada pendekatan AMD yang bercita -cita tinggi. Reka bentuk chiplet yang lebih kompleks ini berbeza dari silikon Navi 31 yang kini digunakan dalam Radeon RX 7900 XTX. Walaupun lelaran sebelumnya GPU dianggap sebagai generasi pertama, ia tidak menggunakan reka bentuk chiplet sebenar seperti pemproses Ryzen baru -baru ini AMD. Walau bagaimanapun, konsepsi Navi 4c yang didedahkan mewakili kemajuan yang ketara, kerana ia menggabungkan beberapa chiples pengiraan, serta chiplets I/O yang berbeza, pada satu substrat tunggal. Imej yang bocor membentangkan 13 chiplets, dengan kemungkinan cip pengawal memori tambahan tidak dipaparkan pada gambar.

Untuk mengesahkan keaslian imej, paten yang berkaitan dengan 2021 membincangkan konsep modulariti dalam pemproses selari diserlahkan. Corak paten rapat menyerupai reka bentuk yang ditunjukkan dalam imej yang bocor, bahkan mencadangkan kemungkinan lebih banyak chiplets di sisi lain dari cawan melintang.

Malangnya, reka bentuk GPU yang dibentangkan dalam imej bocor telah dibatalkan. Ini bersetuju dengan hubungan baru. Walau bagaimanapun, berspekulasi bahawa AMD mengalihkan usaha untuk pembangunan GPU yang terdiri daripada beberapa chiplet pengiraan untuk segmen tinggi kad grafik masa depannya, yang berpotensi dengan rDNA 5.

Walaupun merealisasikan beberapa chiplet pengiraan untuk grafik permainan lebih kompleks daripada pengiraan CPU tradisional, keputusan AMD untuk mengatasi halangan reka bentuk sekarang dan bekerja pada penyelesaian yang lebih baik untuk rDNA 5 dianggap sebagai langkah positif. Ia akan memberi manfaat kepada AMD untuk mempunyai pelan penyelamatan, seperti nod baru untuk versi Navi 31 yang lebih baik.